A JK flip-flop az elektronikai áramkörök egyik legfontosabb építőeleme, különösen a szekvenciális logikai áramkörök területén. Működése lehetővé teszi az adatok tárolását és a bemeneti jelek alapján történő állapotváltozást. Ez a sokoldalúság teszi nélkülözhetetlenné a digitális rendszerek tervezésében.

A flip-flop alapvetően egy bistabil multivibrátor, ami azt jelenti, hogy két stabil állapota van, melyek között a megfelelő bemeneti jelek hatására válthat. A JK flip-flop különlegessége abban rejlik, hogy a J és K bemenetek kombinációival vezérelhető, és a bemenetek mindegyikének más-más funkciója van az állapotváltozás szempontjából.

A JK flip-flop egyik legfontosabb tulajdonsága, hogy kiküszöböli a SR flip-flopnál tapasztalható tiltott állapotot, amikor mindkét bemenet aktív (magas) állapotban van.

A JK flip-flop széleskörűen alkalmazható a digitális elektronikában. Néhány példa:

- Számlálók (bináris, dekád stb.)

- Regiszterek (shift regiszterek, tároló regiszterek)

- Memóriaelemek (statikus RAM-ok építőkövei)

- Szinkronizációs áramkörök

A JK flip-flop megértése elengedhetetlen a komplex digitális áramkörök tervezéséhez és elemzéséhez. A későbbi fejezetekben részletesen bemutatjuk a működését, tervezési szempontjait és gyakorlati alkalmazásait.

A Flip-Flopok alapjai: Áttekintés és típusok

A flip-flopok alapvető építőkövei a digitális elektronikának. Ezek két stabil állapotot képesek megőrizni, így 1 bit információt tárolhatnak. Számos típusa létezik, melyek közül a legfontosabbak: az SR, a D, a T, és a JK flip-flop.

Az SR flip-flop (Set-Reset) bemenetei segítségével állíthatjuk vagy nullázhatjuk az állapotát. A D flip-flop (Data) a bemenetére érkező adatot tárolja el az órajel hatására. A T flip-flop (Toggle) pedig minden órajelre megváltoztatja az állapotát.

A JK flip-flop a leguniverzálisabb típus, mivel az SR flip-flop problémáját, a tiltott állapotot (amikor mindkét bemenet aktív) feloldja. Ezáltal a JK flip-flop minden bemeneti kombinációra definiáltan viselkedik.

A különböző flip-flop típusok eltérő alkalmazásokban használatosak. Például, a D flip-flop regiszterek építésére kiváló, míg a JK flip-flop számlálók és léptetőregiszterek megvalósítására is alkalmas.

A flip-flopok kiválasztásakor figyelembe kell venni a sebességet, a fogyasztást és a vezérlési logikát. A bonyolultabb áramkörök tervezése során gyakran kombinálják a különböző típusú flip-flopokat a kívánt funkcionalitás eléréséhez.

A JK Flip-Flop működési elve: Logikai kapuk és visszacsatolás

A JK flip-flop működésének megértéséhez elengedhetetlen a belső felépítésének vizsgálata. Alapvetően logikai kapuk (általában NAND kapuk) kombinációjából épül fel, melyek visszacsatolással vannak összekötve. Ez a visszacsatolás teszi lehetővé a flip-flop számára, hogy megőrizze az állapotát.

A leggyakoribb implementációban két NAND kapu alkotja az alapvető tároló elemet, melyhez további NAND kapuk kapcsolódnak a J és K bemenetek, valamint az órajel (clock) kezeléséhez. A J bemenet a „set” funkciót, a K bemenet pedig a „reset” funkciót vezérli, de a flip-flop viselkedése az órajel állapotától is függ.

Az órajel változása indítja el az állapotváltozást. Amikor az órajel aktív (például magas szintre vált), a J és K bemenetek értéke határozza meg a kimenet új állapotát. Ha J magas és K alacsony, a flip-flop beállítódik (Q kimenet magas lesz). Ha J alacsony és K magas, a flip-flop visszaállítódik (Q kimenet alacsony lesz). Ha J és K is alacsony, a flip-flop megtartja az előző állapotát. A legérdekesebb eset, amikor J és K is magas. Ebben az esetben a flip-flop átvált (toggle) az ellenkező állapotba.

A JK flip-flop lényege a logikai kapuk visszacsatolt hálózata, amely lehetővé teszi az állapot megőrzését és az órajel által vezérelt állapotváltozást, beleértve a toggle (átváltás) funkciót is.

A visszacsatolási hurkok kritikus szerepet játszanak abban, hogy a flip-flop megőrizze az információt. A kapuk kimenetei befolyásolják a bemeneteiket, létrehozva egy stabil állapotot, amíg az órajel vagy a J és K bemenetek meg nem változtatják ezt az állapotot. A tervezők gondosan választják meg a logikai kapuk típusát és a visszacsatolás módját a kívánt működés elérése érdekében.

A JK flip-flop tervezésekor figyelembe kell venni a propagation delay-t (terjedési késleltetést) is, ami a logikai kapukon áthaladó jel késleltetését jelenti. Ez a késleltetés befolyásolhatja a flip-flop maximális működési frekvenciáját.

Az igazságtábla elemzése: Bemenetek, kimenetek és állapotváltozások

A JK flip-flop igazságtáblája kulcsfontosságú a működésének megértéséhez. A táblázat a J és K bemenetek különböző kombinációit mutatja, valamint az ezekhez tartozó Q(t+1) kimeneti állapotot, azaz a flip-flop következő állapotát, figyelembe véve a jelenlegi Q(t) állapotot.

Nézzük a lehetséges bemeneti kombinációkat:

- Ha J=0 és K=0, a flip-flop megtartja a jelenlegi állapotát, azaz Q(t+1) = Q(t). Ezt „no change” állapotnak nevezzük.

- Ha J=0 és K=1, a flip-flop a „reset” állapotba kerül, azaz Q(t+1) = 0.

- Ha J=1 és K=0, a flip-flop a „set” állapotba kerül, azaz Q(t+1) = 1.

- A legérdekesebb eset, amikor J=1 és K=1. Ekkor a flip-flop „toggle” állapotba kerül, ami azt jelenti, hogy a kimenete megváltozik az ellentétére, azaz Q(t+1) = NOT Q(t).

A JK flip-flop egyik legfontosabb tulajdonsága, hogy a J=1 és K=1 bemeneti kombinációval kiküszöböli a SR flip-flopnál tapasztalható tiltott állapotot, így sokoldalúbbá és megbízhatóbbá téve azt.

Az igazságtábla elemzése során fontos figyelembe venni a clock jel szerepét is. A flip-flop csak a clock jel aktív élekor (emelkedő vagy lemenő) változtatja meg az állapotát, a bemeneteknek ekkor kell stabilnak lenniük a megbízható működéshez.

A JK flip-flop „toggle” funkciója különösen hasznos a bináris számlálók és frekvenciaosztók tervezésénél, mivel lehetővé teszi az állapotok egyszerű váltogatását minden órajel ciklusban.

A JK Flip-Flop belső felépítése: NAND kapukkal implementált áramkör

A JK flip-flop egyik leggyakoribb implementációja NAND kapukkal történik. Ez a felépítés lehetővé teszi a flip-flop univerzális működését, azaz képes a bemeneti jelek alapján beállítani, törölni, megtartani vagy átváltani a kimeneti állapotát.

A NAND kapukkal felépített JK flip-flop általában négy NAND kaput tartalmaz, melyek visszacsatolással vannak összekötve. Ezek a kapuk alkotják a latching (zároló) részt, ami a flip-flop állapotát tárolja. A J és K bemenetek, valamint a clock (órajel) bemenet további NAND kapukon keresztül vezérlik a latch működését.

A J bemenet a „set” (beállítás), a K bemenet pedig a „reset” (törlés) funkciót látja el. Ha J aktív (általában magas szintű), és órajel érkezik, a flip-flop beállítódik (Q kimenet 1 lesz). Hasonlóan, ha K aktív és órajel érkezik, a flip-flop törlődik (Q kimenet 0 lesz). Ha mindkét bemenet aktív (J=1 és K=1), a flip-flop átvált az aktuális állapotából a másikba, ezt hívjuk toggle üzemmódnak.

A NAND kapukkal megvalósított áramkör előnye, hogy könnyen gyártható és elterjedt. A visszacsatolásos hálózat biztosítja, hogy a flip-flop stabil állapotban maradjon, amíg új bemeneti jelek nem érkeznek. Az órajel szinkronizálja a működést, biztosítva, hogy az állapotváltozás csak akkor következzen be, amikor az órajel aktív.

A NAND kapus implementáció esetén a flip-flop működésének megértéséhez elengedhetetlen a kapuk igazságtábláinak és az áramkör visszacsatolásainak alapos elemzése.

A versenyhelyzetek (race conditions) elkerülése érdekében, amelyek a bemenetek szinte egyidejű változása miatt alakulhatnak ki, fontos a megfelelő tervezés és a kapuk terjedési késleltetésének figyelembevétele.

A JK Flip-Flop időzítése: Setup idő, hold idő és propagációs késleltetés

A JK flip-flop működésének megértéséhez elengedhetetlen az időzítési paraméterek ismerete. Ezek a paraméterek határozzák meg, hogy a flip-flop milyen gyorsan és megbízhatóan képes váltani az állapotát.

A setup idő (tSU) az az időtartam, amely alatt a J és K bemeneteknek stabilnak kell lenniük a clock jel élének bekövetkezte előtt. Ha ez az idő nem teljesül, a flip-flop kimenete bizonytalan állapotba kerülhet, ami hibás működést eredményezhet.

A hold idő (tH) az az időtartam, amely alatt a J és K bemeneteknek stabilnak kell maradniuk a clock jel élének bekövetkezte után. Ennek az időnek a megsértése szintén bizonytalan kimenethez vezethet. Általában a hold idő rövidebb, mint a setup idő, de fontos figyelembe venni a tervezés során.

A propagációs késleltetés (tPD) az az idő, ami eltelik a clock él bekövetkezte és a flip-flop kimenetének változása között. Ez a késleltetés korlátozza a flip-flop maximális működési frekvenciáját, és kritikus szerepet játszik a szinkron áramkörök tervezésében.

Ezen időzítési paraméterek ismerete és betartása kulcsfontosságú a megbízható és stabil JK flip-flop alapú áramkörök tervezéséhez. A gyártók adatlapjai részletesen tartalmazzák ezeket az értékeket, amelyeket feltétlenül figyelembe kell venni.

A versenyhelyzet (Race Condition) problémája és megoldásai

A JK flip-flopok egyik legnagyobb kihívása a versenyhelyzet (race condition) kialakulásának lehetősége, különösen akkor, ha a J és K bemenetek egyszerre vannak magasan (logikai 1-en) és a clock jel is magas. Ebben az esetben a flip-flop kimenete elméletileg minden órajel impulzusnál váltania kellene (toggle). A probléma abból adódik, hogy a valós áramkörökben a jelterjedési idő nem nulla, és az egyes kapuk késleltetései között is lehet eltérés.

Ez a késleltetés azt eredményezheti, hogy a flip-flop kimenete többször vált egyetlen órajel impulzus alatt, mielőtt stabilizálódna. Ez nemdeterminisztikus viselkedéshez vezet, ami azt jelenti, hogy nem lehet pontosan megjósolni a flip-flop végső állapotát.

A versenyhelyzet elkerülésének legfontosabb módja az órajel impulzus szélességének korlátozása és a flip-flop terjedési idejének figyelembe vétele.

Több módszer is létezik a versenyhelyzet minimalizálására:

- Élvezérelt flip-flopok használata: Ezek a flip-flopok csak az órajel felfutó vagy lefutó élére reagálnak, ami jelentősen csökkenti a versenyhelyzet kockázatát.

- Master-slave flip-flopok alkalmazása: Ez a konstrukció két flip-flopot tartalmaz sorba kötve, ahol az egyik (master) a teljes órajel idején érzékeli a bemeneteket, a másik (slave) pedig csak az órajel egyik felében (pl. a lefutó élén) frissül. Ez biztosítja, hogy a kimenet csak egyszer változzon egy órajel ciklus alatt.

- Az órajel impulzus szélességének szabályozása: Az órajel impulzusának elegendően rövidnek kell lennie ahhoz, hogy a flip-flop ne tudjon többször váltani.

- Megfelelő tervezés és áramköri elemek kiválasztása: A kapuk késleltetési idejének minimalizálása és az áramkör gondos tervezése szintén segíthet a versenyhelyzet elkerülésében.

A versenyhelyzet elkerülése kritikus fontosságú a megbízható digitális áramkörök tervezésénél, különben a rendszer működése kiszámíthatatlanná válhat.

Master-Slave JK Flip-Flop: A versenyhelyzet kiküszöbölése

A JK flip-flop egyik korai, de fontos továbbfejlesztése a Master-Slave JK flip-flop volt. Ennek célja a versenyhelyzet (race condition) kiküszöbölése, ami a hagyományos JK flip-flopoknál problémát okozhat. A versenyhelyzet akkor lép fel, amikor a bemenetek változása olyan gyorsan történik, hogy a kimenet instabil állapotba kerül, és nem egyértelmű, hogy milyen értéket kellene felvennie.

A Master-Slave felépítés lényegében két JK flip-flop sorba kapcsolása. Az első flip-flop, a „Master”, a bemeneti jeleket a clock jel emelkedő élén fogadja. A kimenetei a „Slave” flip-flop bemeneteire kerülnek. A „Slave” flip-flop azonban csak a clock jel lemenő élén reagál ezekre a bemenetekre.

Ez a kétlépcsős működés biztosítja, hogy amíg a bemeneti jelek változnak, a „Slave” flip-flop izolálva van, így a kimenet stabil marad.

Ennek eredményeként a Master-Slave JK flip-flop megbízhatóbb működést biztosít, különösen magas frekvenciájú alkalmazásokban. Bár a modern flip-flop tervezési technikák, mint például az élvezérelt (edge-triggered) flip-flopok, nagyrészt felváltották a Master-Slave megoldást, a koncepció fontos mérföldkő volt a digitális áramkörök fejlődésében, és segített megérteni a flip-flopok működésének finomságait.

Fontos megjegyezni, hogy a Master-Slave elrendezés a versenyhelyzetet csökkenti, de nem feltétlenül szünteti meg teljesen bizonyos szélsőséges esetekben. Mindazonáltal jelentős előrelépést jelentett a korai digitális áramkörök tervezésében.

Triggerelés típusai: Élére érzékeny és szintérzékeny triggerelés

A JK flip-flop működésének megértéséhez kulcsfontosságú a triggerelés típusainak ismerete. Két fő típust különböztetünk meg: élére érzékeny és szintérzékeny triggerelést.

Szintérzékeny triggerelés esetén a flip-flop kimenete a bemeneti jel szintjének megfelelően változik, amíg a clock jel aktív (magas vagy alacsony). Ez azt jelenti, hogy amíg a clock jel aktív szinten van, a bemenetek változásai hatással lehetnek a kimenetre. Ez problémákat okozhat, például versenyhelyzeteket, amikor a kimenet kiszámíthatatlanul változik a bemenetek gyors változása miatt.

Az élére érzékeny triggerelés sokkal megbízhatóbb. Ebben az esetben a flip-flop csak a clock jel emelkedő (pozitív él) vagy eső (negatív él) élén reagál a bemenetekre. A clock jel többi részében a bemenetek változásai nem befolyásolják a kimenetet. Ez kiküszöböli a versenyhelyzeteket és stabilabb működést biztosít.

A JK flip-flopok többsége élére érzékeny triggerelést használ a megbízható működés érdekében.

Például, egy emelkedő élre érzékeny JK flip-flop csak akkor fogja figyelembe venni a J és K bemeneteket, amikor a clock jel alacsonyról magasra vált. Utána, amíg a clock jel magas, a bemenetek változásai nem befolyásolják a kimenetet. Ezzel a módszerrel pontosabban vezérelhetjük a flip-flop működését.

JK Flip-Flop tervezése: Szempontok és kihívások

A JK flip-flop tervezésekor számos szempontot figyelembe kell venni a megbízható és hatékony működés érdekében. Az egyik legfontosabb a terjedési késleltetés minimalizálása, mivel ez közvetlenül befolyásolja az áramkör maximális működési frekvenciáját. A tervezőknek gondoskodniuk kell arról, hogy a flip-flop a lehető leggyorsabban váltson állapotot a bemeneti jelek változásaira reagálva.

A metastabilitás egy másik kritikus kihívás. Ez akkor fordulhat elő, amikor a J és K bemenetek a órajel élének közelében változnak. Ilyenkor a flip-flop kimenete bizonytalan állapotba kerülhet, ami hibás működést eredményezhet a digitális áramkörben. A tervezőknek olyan technikákat kell alkalmazniuk, mint például a metastabilitás-szűrők, hogy csökkentsék ennek a jelenségnek a hatását.

A JK flip-flop tervezésének egyik legnagyobb kihívása a versenyhelyzetek elkerülése, különösen a bemeneti kombinációk változásakor.

További szempontok közé tartozik a fogyasztás, ami különösen fontos hordozható eszközökben vagy akkumulátoros rendszerekben. A tervezőknek optimális tranzisztorméreteket és alacsony feszültségű működést kell alkalmazniuk a fogyasztás csökkentése érdekében. Végül, a zajvédelem is kulcsfontosságú, mivel a zajos környezetben a flip-flop hibásan válthat állapotot. Megfelelő szűréssel és árnyékolással minimalizálható a zaj hatása.

Aszinkron bemenetek: Preset és Clear funkciók

A JK flip-flopok aszinkron bemenetekkel is rendelkezhetnek, melyek a Preset (PR) és Clear (CLR) funkciókat valósítják meg. Ezek a bemenetek lehetővé teszik a flip-flop állapotának közvetlen, a clock jel figyelmen kívül hagyásával történő beállítását.

Amikor a PR bemenet aktív (általában alacsony szint), a flip-flop kimenete (Q) azonnal 1-re vált, függetlenül a J, K bemenetek állapotától és a clock jel jelenlététől. Hasonlóan, ha a CLR bemenet aktív, a Q kimenet azonnal 0-ra vált. Mindkét aszinkron bemenet felülbírál minden más bemenetet.

A Preset és Clear bemenetek rendkívül hasznosak a flip-flopok inicializálásához, azaz a rendszerindításkor vagy hibahelyzetekben a kívánt kiindulási állapot beállításához.

Fontos megjegyezni, hogy ha mindkét aszinkron bemenet egyszerre aktív, az eredmény nem definiált, és a flip-flop kimenete kiszámíthatatlanul viselkedhet. Ezért kerülni kell ezt az állapotot a tervezés során. A flip-flop adatlapja pontosan leírja, hogy a flip-flop hogyan viselkedik ebben az esetben.

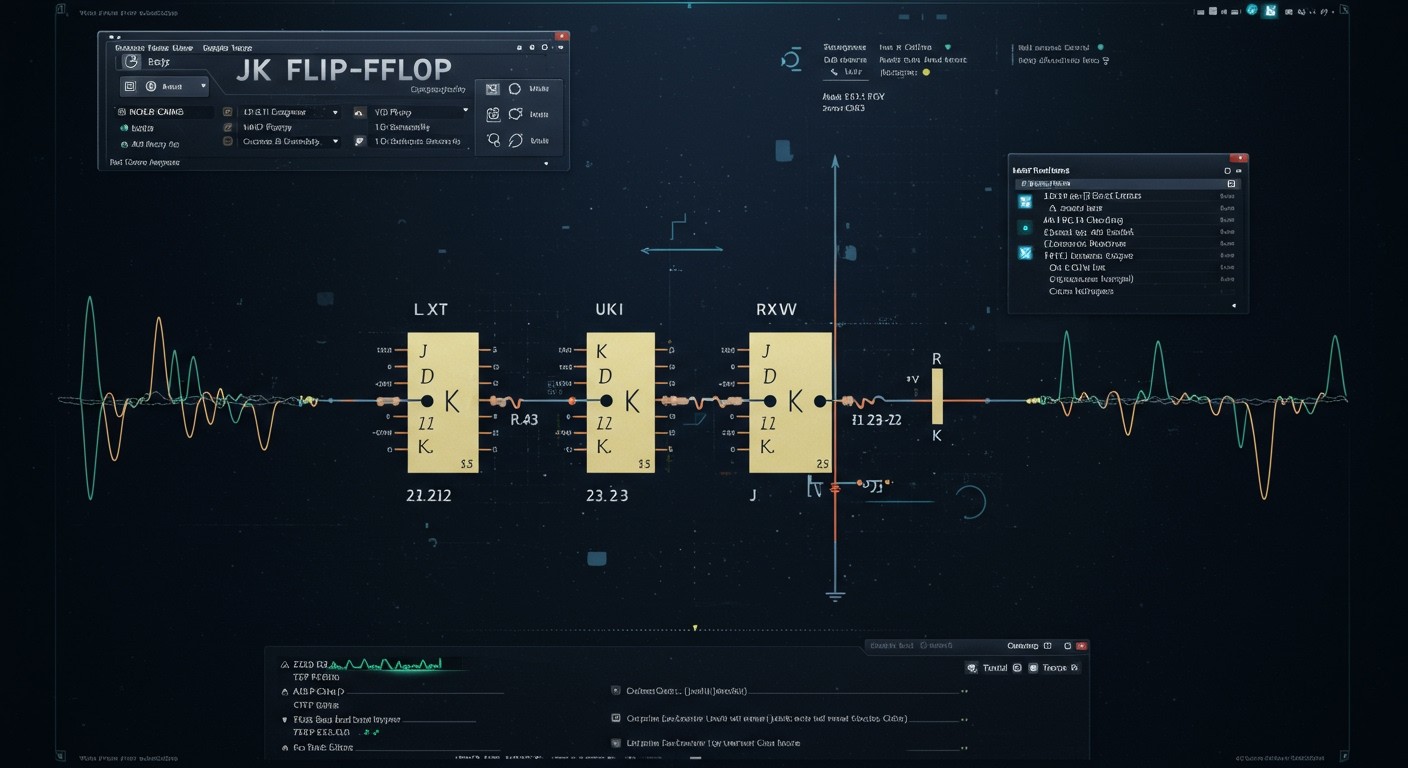

A JK Flip-Flop szimulációja: Szoftveres modellezés

A JK flip-flop működésének megértéséhez és a vele való kísérletezéshez kiváló eszköz a szoftveres szimuláció. Számos elektronikai tervezőprogram, mint például a Multisim, LTspice vagy a TINA, kínál beépített JK flip-flop modelleket, amelyekkel valósághűen szimulálhatjuk a áramkör viselkedését.

Ezek a szimulátorok lehetővé teszik a bemeneti jelek (J, K, Clock) változtatását és a kimeneti jelek (Q, Q’) figyelését. Ezzel a módszerrel könnyen tanulmányozhatjuk a flip-flop működési táblázatát és a különböző bemeneti kombinációk hatásait. A szimuláció során akár tranziensek is vizsgálhatók, ami segít feltárni a flip-flop kapcsolási sebességét és a jelterjedési késleltetést.

A szoftveres modellezés különösen hasznos összetett digitális áramkörök tervezésekor, mivel a segítségével a prototípus építése előtt tesztelhetjük a JK flip-flopokból épülő áramkörök működését, elkerülve ezzel a költséges hibákat.

A szimuláció továbbá lehetővé teszi a különböző flip-flop típusok (pl. Master-Slave JK flip-flop) összehasonlítását és a valós alkatrészek paramétereinek (pl. felfutási idő, lefutási idő) figyelembevételét a tervezés során. A szimulációs eredmények alapján finomíthatjuk a tervezést, optimalizálhatjuk az áramkör teljesítményét és megbízhatóságát.

JK Flip-Flop vs. SR Flip-Flop: Összehasonlítás és különbségek

A JK flip-flop és az SR flip-flop közötti legfőbb különbség a bemenetek viselkedésében rejlik. Az SR flip-flopnál, ha mindkét bemenet (S és R) aktív (általában logikai 1), akkor egy definiálatlan állapot lép fel, ami nem kívánatos. Ezzel szemben a JK flip-flop, amikor mindkét bemenet (J és K) aktív, nem definiálatlan állapotba kerül, hanem a kimeneti állapot átbillen (toggle), azaz a jelenlegi állapotának az ellentétére vált.

Ez az átbillenési képesség teszi a JK flip-flopot sokkal sokoldalúbbá az SR flip-flophoz képest. Például, JK flip-flopokat használhatunk számlálók, shift regiszterek és más komplex szekvenciális áramkörök építéséhez, ahol az állapotok közötti váltás kulcsfontosságú.

Az SR flip-flop definiálatlan állapota a JK flip-flopnál az átbillenési funkcióval van feloldva, ami a JK flip-flop egyik legfontosabb előnye.

Röviden, míg az SR flip-flop egyszerűbb felépítésű, a JK flip-flop a bemeneti kombinációk kezelésében nyújtott nagyobb rugalmassága miatt gyakrabban preferált a gyakorlati alkalmazásokban.

JK Flip-Flop vs. D Flip-Flop: Összehasonlítás és alkalmazási területek

A JK flip-flop és a D flip-flop két alapvető építőelem a digitális elektronikában, de jelentős különbségek vannak közöttük. A D flip-flop egyszerűbb: a bemeneti (D) értékét tárolja a következő órajel hatására. Ezzel szemben a JK flip-flop sokoldalúbb.

A legfontosabb különbség a bemenetek kezelésében rejlik. Ha a JK flip-flop mindkét bemenete (J és K) magas (1), akkor állapotot vált (toggle). Ez a D flip-flopnál nem lehetséges, ami azt jelenti, hogy a JK flip-flop alkalmasabb számlálók és léptetők tervezésére. A D flip-flop ezzel szemben ideális adattárolásra és késleltetésre.

A JK flip-flop „toggle” funkciója, amikor mindkét bemenete aktív, lehetővé teszi komplexebb szekvenciális áramkörök megvalósítását, mint a D flip-flop.

Alkalmazási területeik is eltérőek. A D flip-flopokat gyakran használják regiszterekben és memóriákban, ahol az adatokat egyszerűen tárolni és átvinni kell. A JK flip-flopok viszont előnyösebbek szinkron és aszinkron számlálókban, frekvenciaosztókban, valamint olyan áramkörökben, ahol szükség van az állapotváltásra.

Számlálók építése JK Flip-Flopokkal: Aszinkron és szinkron számlálók

A JK flip-flopok kulcsfontosságú építőelemek a számlálók tervezésében. Két fő típust különböztetünk meg: az aszinkron (vagy ripple) és a szinkron számlálókat. Az aszinkron számlálókban az egyes flip-flopok kimenete hajtja meg a következő flip-flop órajel bemenetét. Ez azt jelenti, hogy a flip-flopok nem egyszerre váltanak, hanem egy „hullámzó” effektus jön létre, ahogy a jel végighalad a láncon.

Ezzel szemben a szinkron számlálókban minden flip-flop ugyanazt az órajelet kapja. Ez biztosítja, hogy az összes flip-flop egyszerre váltson, ami gyorsabb és megbízhatóbb működést eredményez, mint az aszinkron számlálók esetében. A szinkron számlálók tervezése bonyolultabb, de a jobb teljesítmény miatt gyakran előnyösebbek.

Az aszinkron számlálók egyszerűbbek és könnyebben megvalósíthatók, ezért gyakran használják őket alacsony frekvenciás alkalmazásokban. A szinkron számlálók viszont alkalmasabbak nagy sebességű alkalmazásokhoz, ahol a precíz időzítés kritikus fontosságú.

A JK flip-flopok lehetővé teszik a számlálók fel- és leszámlálási funkcióinak megvalósítását is. A JK bemenetek megfelelő beállításával a flip-flop vagy vált, vagy megtartja az állapotát, vagy beállítja a kimenetet logikai magasra vagy alacsonyra. Ez a rugalmasság teszi a JK flip-flopokat ideális választássá sokféle számláló alkalmazáshoz.

A JK flip-flopok sokoldalúsága lehetővé teszi mind aszinkron, mind szinkron számlálók hatékony megvalósítását, amivel a digitális áramkörök tervezésének nélkülözhetetlen elemeivé válnak.

Például, egy 4 bites bináris aszinkron számlálóhoz négy JK flip-flop szükséges, ahol az első flip-flop órajele a külső órajel, a többi flip-flop órajele pedig az előző flip-flop kimenete. Egy szinkron számlálóhoz bonyolultabb logikai kapukra van szükség, de az összes flip-flop egyszerre vált, ami jelentősen javítja a teljesítményt.

Regiszterek építése JK Flip-Flopokkal: Shift regiszterek és tárolók

A JK flip-flopok kiválóan alkalmasak regiszterek építésére, melyek az elektronikus rendszerek alapvető építőkövei. Két fő típusa a shift regiszter és az egyszerű tároló regiszter. Mindkettő a JK flip-flopok sorba kapcsolásával valósul meg.

A shift regiszterek lényege, hogy a bemenő adatot bitenként léptetik tovább a flip-flopokon keresztül. Minden órajelciklusban a legelső flip-flop felveszi az új bemenő értéket, a többi pedig az előző flip-flop kimenetét. Ezzel az adatok „elcsúsznak” a regiszterben. Shift regiszterek használhatók soros adatok párhuzamos formátumúvá alakítására (serial-to-parallel conversion) és fordítva, párhuzamos adatok soros formátumúvá alakítására (parallel-to-serial conversion). Ezen felül, késleltetésre is alkalmazhatók, hiszen az adat csak néhány órajelciklus után jelenik meg a kimeneten.

A tároló regiszterek (vagy egyszerűen regiszterek) célja az adatok tárolása. Itt minden flip-flop egy-egy bitet tárol az adatokból. A JK flip-flopok J és K bemenetei megfelelően vezérelve teszik lehetővé az adatok beírását és megtartását. Gyakran engedélyező bemenetet (enable) is használnak, ami megakadályozza az adatok véletlen felülírását.

A JK flip-flopokból épített regiszterek kulcsszerepet játszanak a számítógépek memóriájában, aritmetikai és logikai egységeiben, valamint egyéb digitális áramkörökben.

A regiszterek tervezése során figyelembe kell venni az órajel frekvenciáját, a tárolandó bitek számát, és a szükséges funkcionalitást (pl. shiftelés, párhuzamos betöltés). Az aszinkron és szinkron bemenetek helyes használata is elengedhetetlen a megbízható működéshez.

Például, egy 4-bites shift regiszter négy JK flip-flopból áll sorba kötve, ahol az első flip-flop bemenete a soros adatbemenet, és az utolsó flip-flop kimenete a soros adatkimenet. Egy 4-bites tároló regiszter szintén négy JK flip-flopból áll, de itt a flip-flopok J és K bemenetei a párhuzamos adatbemenetekhez vannak kötve, és az órajel vezérli az adatok beírását.

Állapotgépek tervezése JK Flip-Flopokkal: Moore és Mealy modellek

Az állapotgépek tervezése során a JK flip-flop egy rendkívül hasznos építőelemnek bizonyul. Két elterjedt modell, a Moore és a Mealy modell, különböző megközelítéseket kínál az állapotgépek implementálására, és mindkettő hatékonyan használható JK flip-flopokkal.

Moore modell: Ebben a modellben a kimenet kizárólag az aktuális állapottól függ. Ez azt jelenti, hogy a kimenet csak akkor változik, amikor az órajel élén az állapot is megváltozik. A JK flip-flopok itt arra használatosak, hogy az állapotokat tárolják, és a megfelelő logikai áramkörök (például NAND vagy NOR kapuk) generálják a flip-flopok bemeneteit (J és K), biztosítva a helyes állapotátmeneteket. A Moore gépek tervezése általában egyszerűbb, mivel a kimenet független a bemenettől, így a hibakeresés is könnyebb lehet.

Mealy modell: Ezzel szemben a Mealy modellben a kimenet nemcsak az aktuális állapottól, hanem a bemenettől is függ. Ez azt jelenti, hogy a kimenet aszinkron módon változhat, amikor a bemenet változik, *akár az órajel élétől függetlenül is*. A JK flip-flopok itt is az állapotok tárolására szolgálnak, de a kimeneti logikai áramkörök bonyolultabbak, mivel a bemeneteket is figyelembe kell venniük. A Mealy gépek gyakran kevesebb állapottal megvalósíthatók, mint a Moore gépek, de a tervezés és a hibakeresés bonyolultabb lehet a bemenetfüggő kimenetek miatt.

A JK flip-flopok J és K bemeneteinek vezérlése Karnaugh-táblák (K-map) segítségével optimalizálható. Ez a módszer segít minimalizálni a logikai kapuk számát, ami egyszerűbb és hatékonyabb áramköröket eredményez. A K-map segítségével meghatározzuk a J és K bemenetekhez szükséges logikai kifejezéseket az adott állapotátmenetekhez.

A JK flip-flopok kiválóan alkalmasak állapotgépek megvalósítására a sokoldalúságuk miatt, mivel a J és K bemenetekkel könnyen vezérelhetők az állapotátmenetek, mind a Moore, mind a Mealy modellben.

Például, ha egy egyszerű számlálót tervezünk, a JK flip-flopokat kaszkádba köthetjük, ahol az egyik flip-flop kimenete a következő flip-flop órajeleként szolgál. A J és K bemenetek megfelelő beállításával (pl. mindkettőt 1-re állítva) biztosíthatjuk, hogy a flip-flop minden órajel élén átforduljon, létrehozva a kívánt számlálási sorrendet.

Frekvenciaosztók építése JK Flip-Flopokkal

A JK flip-flop egyik leggyakoribb alkalmazása a frekvenciaosztók építése. Ennek alapja, hogy a JK flip-flop T flip-flopként konfigurálható, ha mindkét bemenetét (J és K) logikai 1-re állítjuk. Ebben az esetben a kimenet minden órajel impulzusra vált, azaz a kimeneti frekvencia fele lesz a bemeneti órajel frekvenciájának.

Frekvenciaosztó áramkörök kaszkádba kötött JK flip-flopokból épülnek fel. Minden egyes flip-flop felezi a bemeneti frekvenciát, így n darab flip-flopból álló lánc a bemeneti frekvenciát 2n-nel osztja el.

Ez a tulajdonság teszi a JK flip-flopokat nélkülözhetetlenné olyan alkalmazásokban, ahol pontosan meghatározott frekvenciájú jelekre van szükség, például digitális órákban, számlálókban és kommunikációs rendszerekben.

A frekvenciaosztók tervezésénél fontos figyelembe venni a flip-flopok terjedési késleltetését, mivel ez befolyásolhatja a maximális működési frekvenciát. Továbbá, a kaszkádba kötött flip-flopok esetén a jel integritásának megőrzése érdekében megfelelő illesztést kell biztosítani.

Adattárolás JK Flip-Flopokkal: Memóriacellák alapjai

A JK flip-flop kulcsfontosságú szerepet játszik az adattárolásban, különösen a memóriacellák építésében. Míg egyetlen JK flip-flop csak egy bit információt képes tárolni (0 vagy 1), ezek kombinációja alkotja a regisztereket és memóriabankokat.

A flip-flopok stabilitása kritikus a megbízható adattárolás szempontjából. A JK flip-flop „set” (beállít) és „reset” (visszaállít) bemenetei lehetővé teszik az adat írását a flip-flopba, míg a „clock” (órajel) bemenet szinkronizálja az adatváltozásokat. Ez megakadályozza a véletlenszerű vagy nem kívánt állapotváltozásokat.

A JK flip-flopokból épített memóriacellák az elektronikus rendszerek alapvető építőkövei, lehetővé téve az adatok tárolását és későbbi előhívását.

A modern memóriachipek, mint például a RAM (Random Access Memory), rengeteg JK flip-flop vagy más hasonló tárolóelem kombinációjából állnak. Ezek a cellák mátrixszerűen vannak elrendezve, és címezhetők, így a processzor közvetlenül hozzáférhet a tárolt adatokhoz. Az írás és olvasás műveletek a flip-flopok állapotának beállításán és érzékelésén alapulnak.

A JK flip-flopok alkalmazása a memóriacellákban biztosítja a gyors és megbízható adathozzáférést, ami elengedhetetlen a számítógépek és más digitális eszközök működéséhez. A tervezés során figyelembe kell venni a flip-flopok fogyasztását és kapcsolási sebességét is, hogy optimalizáljuk a memória teljesítményét.

Gyakorlati alkalmazások: Számítógépek, vezérlőrendszerek és egyéb területek

A JK flip-flop sokoldalúsága révén számos területen alapvető építőelemként funkcionál. A számítógépek működésétől kezdve az ipari vezérlőrendszereken át, egészen a telekommunikációs eszközökig mindenhol megtalálható.

A számítógépekben a JK flip-flopokat elsősorban regiszterek és számlálók megvalósítására használják. A regiszterek adatok ideiglenes tárolására szolgálnak, míg a számlálók bináris értékeket növelnek vagy csökkentenek, melyek a processzor működéséhez elengedhetetlenek. A JK flip-flopok itt a memóriacellák alapját képezhetik, biztosítva az adatok megbízható tárolását és visszakeresését.

Az ipari vezérlőrendszerekben a JK flip-flopok a folyamatok automatizálásában játszanak kulcsszerepet. Például, egy futószalag vezérlésében a flip-flopok érzékelőktől kapott jeleket tárolhatnak, és ezek alapján vezérelhetik a motorokat vagy más alkatrészeket. A flip-flopok emellett logikai kapukkal kombinálva komplex vezérlési algoritmusokat valósíthatnak meg.

A JK flip-flopok alkalmazása a vezérlőrendszerekben lehetővé teszi a pontos és megbízható működést, növelve a termelékenységet és csökkentve a hibák lehetőségét.

A távközlésben a JK flip-flopokat frekvenciaosztók, modulátorok és demodulátorok építésére használják. A frekvenciaosztók a bemeneti jel frekvenciáját csökkentik, ami elengedhetetlen a stabil és pontos jelátvitelhez. A modulátorok és demodulátorok pedig az adatok átviteléhez szükséges jelalakításban játszanak fontos szerepet.

Más területeken is találkozhatunk JK flip-flopokkal. Például, a digitális órákban a másodperc-, perc- és óraszámlálók építésére használják őket. Az orvosi eszközökben a mérési adatok tárolására és feldolgozására alkalmazzák. A játékautomatákban pedig a véletlenszerű események generálásában játszanak szerepet.

Összefoglalva, a JK flip-flop a digitális elektronika egy rendkívül sokoldalú és nélkülözhetetlen eleme. Széleskörű alkalmazhatósága a megbízhatóságának, egyszerű használatának és a különböző logikai funkciók megvalósítására való képességének köszönhető.